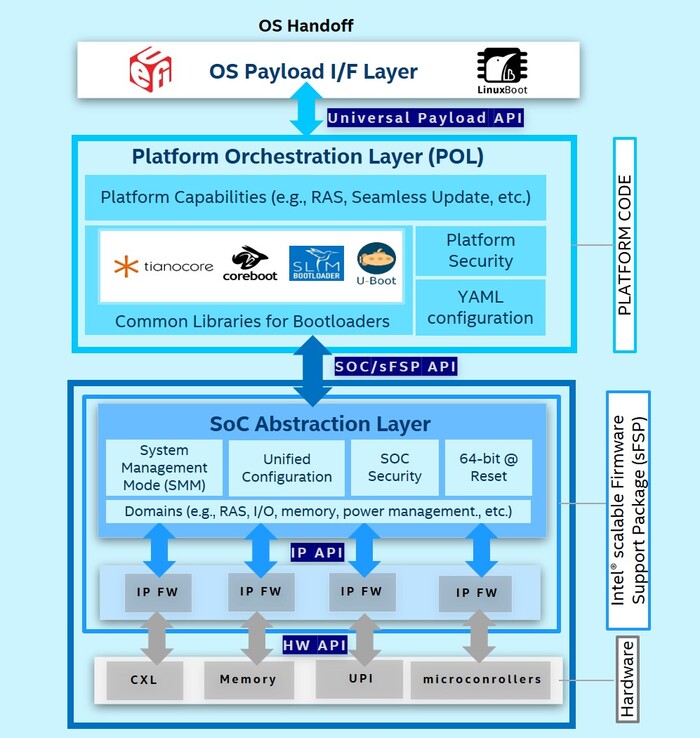

USF имеет модульную структуру, не привязанную к конкретным решениям и позволяющую использовать различные существующие проекты, реализующие стадии инициализации оборудования и загрузки, такие как UEFI-стек TianoCore EDK2, минималистичную прошивку Slim Bootloader, загрузчик U-Boot и платформу CoreBoot. В качестве payload-окружений, применяемых для поиска загрузчика и передачи управления операционной системе, могут применяться интерфейс UEFI, прослойка LinuxBoot (для прямой загрузки ядра Linux), VaultBoot (верифицированная загрузка) и гипервизор ACRN. Для операционных систем предоставляются типовые интерфейсы, такие как ACPI, UEFI, Kexec и Multi-boot.

USF выделяет отдельный слой для поддержки оборудования (FSP, Firmware Support Package), который взаимодействует с универсальным и настраиваемым слоем оркестровки платформы (POL, Platform Orchestration Layer) через общий API. FSP абстрагирует такие операции, как сброс CPU, инициализация оборудования, работа с SMM (System Management Mode), аутентификация и верификация на уровне SoC. Слой оркестровки упрощает создание интерфейсов ACPI, поддерживает типовые библиотеки загрузчиков, позволяет использовать язык Rust для создания защищённых компонентов прошивки и даёт возможность определять конфигурацию при помощи языка разметки YAML. На уровне POL также выполняется аттестация (подтверждение подлинности), аутентификация и организация безопасной установки обновлений.

Ожидается, что новая архитектура позволит:

- Снизить сложность и стоимость разработки прошивок для новых устройств за счёт повторного задействования кода готовых типовых компонентов, модульной архитектуры, не привязанной к конкретным загрузчикам, и возможности использования универсального API для настройки модулей.

- Повысить качество и безопасность прошивок, благодаря применению верифицируемых модулей взаимодействия с оборудованием и более безопасной инфраструктуры для проверки подлинности и верификации прошивок.

- Использовать различные загрузчики и payload-компоненты, в зависимости от решаемых задач.

- Ускорить продвижение новых технологий и сократить цикл разработки — разработчики могут сосредоточиться только на добавлении специфичной функциональности, в остальном используя готовые проверенные компоненты.

- Масштабировать разработку прошивок для различных смешанных вычислительных архитектур (XPU), например, включающих помимо CPU встроенный дискретный графический ускоритель (dPGU) и программируемые сетевые устройства для ускорения выполнения сетевых операций в ЦОД, обеспечивающих работу облачных систем (IPU, Infrastructure Processing Unit).

Источник: http://www.opennet.ru/opennews/art.shtml?num=56239