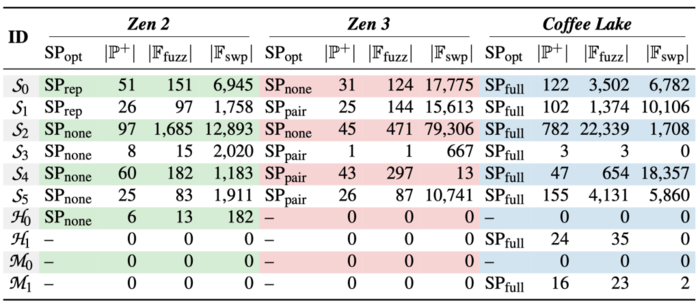

Работа метода продемонстрирована на системах AMD Zen 2 и Zen 3 с памятью DDR4 от трёх ведущих производителей (Samsung, Micron и SK Hynix). Атака успешно позволяет обойти реализуемый в чипах памяти механизм TRR (Target Row Refresh), нацеленный на защиту от искажения ячеек памяти в соседних строках. По оценке исследователей системы на базе CPU AMD Zen 3 более уязвимы, чем системы с процессорами Intel Coffee Lake, и их проще и эффективнее атаковать. На системах AMD Zen 2 искажения ячеек удалось добиться для 7 из 10 протестированных чипов DDR4, а на системах Zen 3 для 6 из 10. Исследователями также проанализирована возможность совершения атаки на системы AMD Zen 4 с памятью DDR5, но разработанный для DDR4 метод атаки удалось успешно воспроизвести лишь на 1 из 10 протестированных чипов памяти DDR5, при этом сама возможность атаки не исключается, но требует разработки более эффективных шаблонов чтения, подходящих для устройств DDR5.

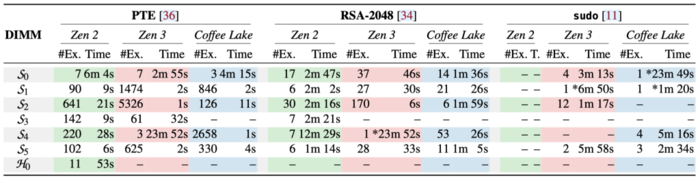

Для работы с чипами AMD удалось адаптировать ранее разработанные эксплоиты, меняющие содержимое записей в таблице страниц памяти (PTE, page table entry) для получения привилегии ядра, обходящие проверку пароля/полномочий через модификацию памяти процесса sudo и повреждающие хранящийся в памяти открытый ключ RSA-2048 в OpenSSH для воссоздания закрытого ключа. Атаку на страницы памяти удалось воспроизвести на 7 из 10 протестированных чипов DDR4, атаку на ключ RSA — на 6 чипах, а атаку на sudo — на 4 чипах, при этом время атаки составило 164, 267 и 209 секунд, соответственно.

Метод также может быть применим для атаки на систему через браузеры, для внесения изменений из виртуальных машин или для организации атаки по сети. На GitHub под лицензией MIT размещён исходных код инструментария DARE для обратного инжиниринга раскладки адресов в памяти DRAM, а также два набора утилит для fuzzing-тестирования искажения битов в памяти — ddr4_zen2_zen3_pub для чипов DDR4 (Zen 2 and Zen 3) и ddr5_zen4_pub для чипов DDR5 (Zen 4), которые могут использоваться для проверки своих систем на подверженность атаке.

Для искажения битов применяется метод RowHammer, который основывается на том, что в памяти DRAM, которая представляет собой двухмерный массив ячеек, состоящих из конденсатора и транзистора, выполнение непрерывного чтения одной и той же области памяти приводит к флуктуации напряжения и аномалиям, вызывающим небольшую потерю заряда соседних ячеек. Если интенсивность чтения большая, то соседняя ячейка может потерять достаточно большой объём заряда и очередной цикл регенерации не успеет восстановить её первоначальное состояние, что приведёт к изменению значения сохранённых в ячейке данных. В ходе исследователя выявлены особенности применяемых в процессорах AMD механизмов маппинга физической памяти и синхронизации с обновлением памяти, позволившие воссоздать низкоуровневую адресацию DRAM, определить адреса соседних ячеек, разработать методы обхода кэширования, вычислить шаблоны и частоту операций, приводящих к потере заряда.

Для защиты от RowHammer производители чипов применяют механизм TRR (Target Row Refresh), который блокирует искажение ячеек в частных случаях, но не защищает от всех возможных вариантов атаки. Наиболее эффективным методом защиты остаётся использование памяти с кодами коррекции ошибок (ECC), которые существенно усложняют, но полностью не исключают проведение атак класса RowHammer. Снизить вероятность успешной атаки также позволяет увеличение частоты регенерации памяти.

Компания AMD опубликовала отчёт о проблеме, в котором говорится, что в процессорах AMD используются контроллеры памяти, соответствующие спецификациям DDR, и так как успешность атаки зависит в основном от настроек системы и DRAM-памяти, с вопросами об устранении проблемы следует обращаться к производителям памяти и систем. Из существующих способов усложнения совершения атак класса Rowhammer упоминается использование ECC-памяти, повышение частоты регенерации памяти, отключение режима отложенной регенерации и использование процессоров с контроллерами, поддерживающими режим MAC

(Maximum Activate Count) для DDR4 (1, 2 и 3 поколение AMD EPYC «Naple», «Rome» и «Milan») и RFM (Refresh Management) для DDR5 (4 поколение AMD EPYC).

Источник: http://www.opennet.ru/opennews/art.shtml?num=60850