VeriGPU позиционируется как специализированный процессор (ASIC), оптимизированный для ускорения вычислений, связанных с системами машинного обучения. В планах упоминается обеспечение совместимости с фреймворком глубинного машинного обучения PyTorch и реализация возможности разработки приложений для VeriGPU с использованием API HIP (Heterogeneous-Compute Interface). В дальнейшем не исключается добавление поддержки и других API, таких как SYCL и NVIDIA CUDA.

GPU развивается на основе набора команд RISC-V, но итоговая внутренняя архитектура набора команд GPU слабо совместима с RISC-V ISA, так как в ситуациях, когда проектирование GPU не укладывается в представление RISC-V, не ставится задача сохранение совместимости с RISC-V. Разработка сфокусирована на возможностях, необходимых для систем машинного обучения, поэтому для сокращения размера и сложности матрицы чипа используется только формат вычислений с плавающей запятой BF16 и доступны лишь востребованные для машинного обучения операции с плавающей запятой, такие как exp, log, tanh и sqrt.

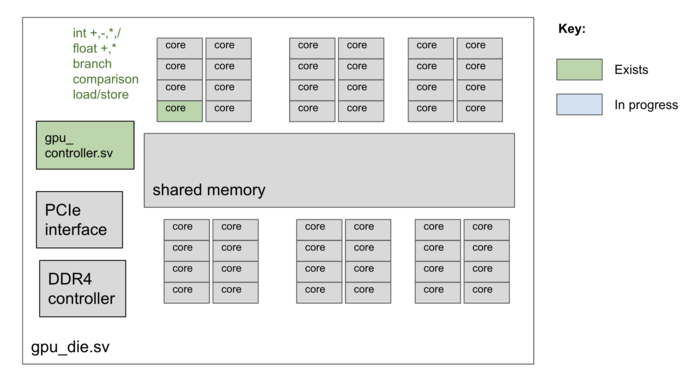

Из уже доступных компонентов называются контроллер GPU, APU (Accelerated Processing Unit) для целочисленных операций («+»,»-«,»/»,»*»), блок для операций с плавающей запятой («+»,»*») и блок обеспечения ветвления. Для создания приложений предлагается ассемблер и поддержка компиляции кода на C++ на базе LLVM. Из планируемых возможностей выделяются параллельное выполнение инструкций, кэширование памяти данных и инструкций, операции SIMT (Single instruction multiple thread).

Источник: http://www.opennet.ru/opennews/art.shtml?num=57074